Silicon

Features

- Dynamic Per Bit Timing Alignment, Tracking and DeSkew

- Patented Multi-phase Multi-grain Dynamic Per Bit Timing Alignment

- Low jitter, 64 phase, Coarse grain, Fine grain, High resolution

- Adaptive Per Bit On Die Termination

- Patented Per Bit Dynamic On Die Impedance Termination

- Automated, PVT invariant, 35-70Ohms board/package trace impedance matching

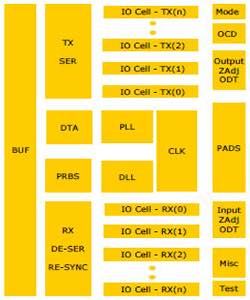

Transmit

- Patented Low Power High Bandwidth Single-ended DDRx Tx

- Multi-level Pre-emphasis, Low latency

- Variable data widths, JEDEC HSTL standard

Receive

- Patented Low Swing High Bandwidth Single-ended DDRx Rx

- Low Swing, High Sensitivity, Low latency

- Variable data widths, JEDEC HSTL standard

Clocking

- Patented Low Power Multi-Phase Timing for High Speed Single-ended IO

- Low Power, Low Jitter, Wide range On-Chip PLL

- Low Power, Low Jitter, Wide range On-Chip DLL

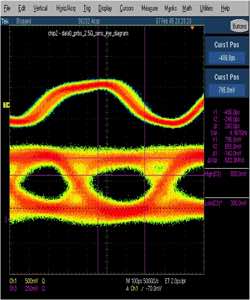

Signal Integrity

- ISI, SSO, Crosstalk, Clock Jitter

- Pwr/gnd bounce, ESD, EMI, PVT

- Pkg/Board via/trace/RLC

Reference Design

- FR4, multi-layer, 3"/5"/15" traces, 3/5 vias

- Chip-chip, chip-connector-chip, chip-DIMM-chip, Design/Simulation models

- Schematic/GDSII/HDL DB, P&R and SI guidelines

- Test/characterization guidelines

- Package/Board design guidelines

- COT/ASIC flow integration guidelines.